半導體產業全解析:從供應鏈到未來技術發展

引言

半導體產業是現代科技發展的核心,影響人工智慧(AI)、雲端運算、自駕車等各大領域。隨著摩爾定律逐漸面臨極限,3DIC 和 CoWoS 先進封裝技術成為突破性能瓶頸的關鍵。本篇文章將從半導體產業鏈、製造流程、封裝技術到未來發展趨勢,深入解析這個影響全球科技格局的關鍵產業。

Insights

- AI 晶片與 HPC 推動封裝技術升級

NVIDIA、AMD 等企業持續採用 CoWoS 和 3DIC 技術,台積電也在積極擴充產能。根據 IDC 的預測,2025 年全球半導體市場將成長 15%,其中記憶體領域預計增長超過 24%,主要受益於 AI 加速器對高階產品如 HBM3、HBM3e 的需求提升。 - 摩爾定律受限,Chiplet 與異質整合成主流

隨著半導體製程進入 3nm 及以下技術門檻,截至 2025 年,台積電已成功量產 2 奈米製程,並積極研發 1.4 奈米技術。隨著製程微縮的挑戰增加,業界轉向 Chiplet(小晶片)架構與 3DIC 封裝,透過異質整合技術提升效能並降低成本,顯示先進製程技術持續突破。而三星則採用GAA技術,在3奈米製程與台積電競爭。英特爾則計劃2024年推出Intel 4(7奈米等級)製程。摩爾定律的延續變得困難,業界轉向 Chiplet(小晶片架構)與 3DIC 封裝,透過異質整合技術提升效能、降低成本。 - 全球半導體供應鏈重組,台積電保持領導地位

美中科技戰推動各國半導體政策轉向自主化,如 美國 CHIPS Act、歐洲半導體法案,但台積電持續擴充 CoWoS 產能,以滿足 AI 與 HPC 市場的需求。預計到 2026 年,CoWoS 年產能將達到 100 萬片,NVIDIA 預計占據 65% 的產能,其次是博通和 AMD,預計持續主導 AI 晶片供應鏈至少五年。

一、半導體產業鏈解析:上游、中游、下游

1. 上游:IC 設計與材料供應

主要企業: 高通(Qualcomm)、聯發科(MediaTek)、輝達(NVIDIA)

- IC 設計(Fabless):負責晶片電路設計,無需自建晶圓廠。

- 電子設計自動化(EDA):如 Synopsys、Cadence,提供電路設計工具。

- 矽智財(IP):ARM、Imagination,提供標準化電路模組。

- 材料供應:高純度矽晶圓(環球晶)、光阻劑、蝕刻材料等。

2. 中游:晶圓製造(Foundry)

主要企業: 台積電(TSMC)、三星(Samsung)、聯電(UMC)

- 晶圓代工:台積電是全球最大晶圓代工廠,市占率領先。

- 設備供應商:如 ASML(EUV 曝光機)、Lam Research(蝕刻機)。

3. 下游:IC 封裝與測試(OSAT)

主要企業: 日月光(ASE)、矽品、京元電子(KYEC)

- 封裝(Assembly):保護裸晶,提升散熱與導電性能。

- 測試(Testing):確保晶片品質,檢測功能是否符合標準。

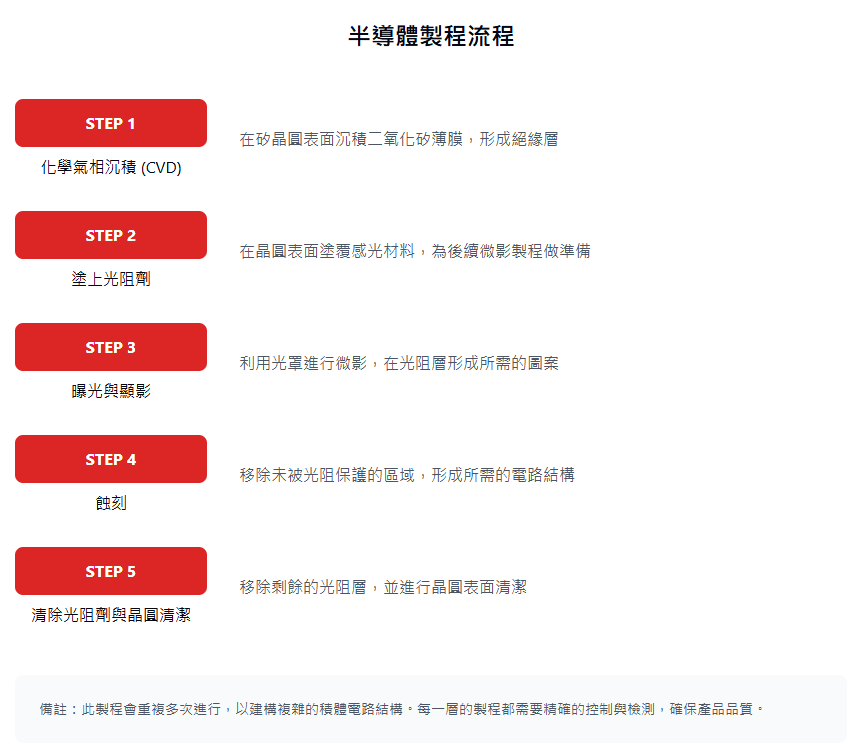

二、半導體製造流程解析

1. IC 設計(Design)

IC 設計(Integrated Circuit Design)是半導體產業鏈的第一步,決定了晶片的架構、功能及效能。高效能計算(HPC)、人工智慧(AI)和車用電子的發展,都驅動了更先進的 IC 設計需求。設計企業利用 EDA 軟體 完成電路設計,再將設計圖交給晶圓廠生產。

IC 設計流程

- 架構規劃(Architecture Planning):確定晶片應用領域,如 AI、5G、HPC 或消費電子。

- 邏輯設計(Logic Design):使用 RTL(Register Transfer Level)描述電路運作邏輯。

- 電路設計(Circuit Design):優化電路結構,確保功耗、效能、面積(PPA)達到最佳平衡。

- 物理設計(Physical Design):將邏輯設計轉換為物理佈局,包括佈線與元件放置。

- 驗證與模擬(Verification & Simulation):進行時序分析、功耗模擬及功能驗證,確保晶片設計無誤。

- 流片(Tape-out):最終設計完成後,送往晶圓代工廠(如台積電、三星)製造。

EDA 與矽智財(IP)

- 電子設計自動化(EDA) 工具如 Synopsys、Cadence、Mentor Graphics,幫助設計工程師快速開發與驗證 IC。

- 矽智財(IP,Intellectual Property) 供應商如 ARM、Imagination,提供標準化 IP 模組,縮短開發時間。

IC 設計技術發展趨勢

- AI 晶片需求提升,推動 NPU(神經處理單元)與 TPU(張量處理單元)技術創新。

- Chiplet(小晶片)架構,透過異質整合提升效能,降低成本。

- 自適應運算技術(Adaptive Computing),如 FPGA(可程式邏輯閘陣列)應用擴展。

2. 晶圓製造(Wafer Fabrication)

- 化學氣相沉積 (CVD):在矽晶圓表面沉積二氧化矽薄膜,形成絕緣層,確保沉積均勻性。

- 光阻製程:塗布感光材料,準備微影製程,厚度需精確控制。

- 微影製程:使用 EUV 技術,解析度達 3nm 以下,精確轉印電路圖形。

- 蝕刻製程:形成電路結構,區分乾式與濕式蝕刻,確保精確圖形轉移。

- 離子植入:改變矽晶特性,控制導電性,確保精確能量植入。

- 化學機械研磨 (CMP):使用拋光技術平坦化晶圓表面,確保多層電路堆疊的精準性,提升製程良率。

3. IC 封裝(Packaging)

- 線鍵合(Wire Bonding):傳統封裝技術,以金線連接晶片與基板。

- 覆晶封裝(Flip-Chip):直接連接封裝基板,提升訊號傳輸效率。

- 系統級封裝(SiP):多顆晶片整合,提高運算效能。

4. IC 測試(Testing)

測試晶片功能與品質,確保符合市場規格。

三、3DIC 與 CoWoS 先進封裝技術

1. 3DIC 和 CoWoS 是什麼?

3DIC(3D Integrated Circuit)

- 利用矽穿孔(TSV)技術,垂直堆疊晶片,降低訊號延遲,提升效能。

CoWoS(Chip-on-Wafer-on-Substrate)

- 由台積電開發,屬於 2.5D 封裝技術,透過中介層(Interposer)連接 GPU、HBM 記憶體。

- 主要應用於 AI、HPC(高效能運算)、雲端伺服器。

2. CoWoS 市場現況與趨勢

- AI 需求飆升:NVIDIA、AMD 廣泛採用 CoWoS 技術,導致產能供不應求。

- 台積電領導地位:台積電正在加速擴充 CoWoS 產能,預計到 2025 年底,每月產能將提高至超過 6 萬片,應對 AI 晶片需求。

- 競爭對手發展:英特爾(Intel)推出 Foveros 3D 封裝技術,三星積極發展 X-Cube 技術。

3. NVIDIA 最新動態與 AI 晶片影響

NVIDIA 的最新 AI 晶片 Blackwell 採用了台積電的 CoWoS-L 封裝技術,以提升運算性能。NVIDIA 執行長黃仁勳表示,公司對先進封裝技術的需求持續增長,並正在調整技術以滿足新產品的需求。

- H100、H200 採用 CoWoS 提升 AI 運算

- AI 伺服器市場帶動先進封裝技術需求

- 市場競爭與供應鏈優化策略

4. 投資機會

四、半導體未來發展趨勢

1. 摩爾定律挑戰與創新

隨著製程微縮的物理極限接近,3DIC 技術和 Chiplet 架構成為提升晶片性能的主要策略。透過異質整合,不同功能的晶片可以在同一封裝中協同工作,提升整體效能並降低成本。

- 3DIC 技術 取代傳統製程微縮,提升晶片效能。

- Chiplet 架構:透過 CoWoS 封裝整合多顆晶片,提高運算效率。

2. AI、HPC 推動高效能晶片需求

AI 和 HPC 的快速發展,特別是在雲端運算和自駕車等領域,對高效能晶片的需求持續攀升。這推動了先進製程和封裝技術的研發與應用,以滿足市場對高性能和低功耗的要求。

- AI 訓練與推論 需要更強大的 GPU、TPU,加速 CoWoS 應用。

- HPC(高效能運算) 擴展至自駕車、5G 網路、元宇宙應用。

3. 車用半導體與新材料技術

- 電動車(EV) 帶動功率半導體需求,如 SiC(碳化矽)、GaN(氮化鎵)。

- 智慧車載系統 需要高效能 MCU、感測器與 AI 晶片。

4. 全球供應鏈變革

- 美中科技戰影響:美國《CHIPS and Science Act》推動本土製造。

- 台積電全球佈局:美國亞利桑那、日本熊本等地建立晶圓廠。

五、結論

半導體產業涵蓋從設計、製造到封裝測試的完整供應鏈,並受到技術創新、AI 崛起、電動車需求與地緣政治影響。未來,3DIC、先進封裝、Chiplet、AI 晶片技術將持續驅動半導體產業升級。台積電的 CoWoS 技術將在 AI 浪潮中扮演關鍵角色,而其他競爭對手也將加速布局。半導體產業仍將是全球科技競爭的核心戰場。

常見問題 (FAQ)

Q1: 為什麼 AI 晶片需要 CoWoS?

A: AI 運算需要高效能與低延遲,CoWoS 可提供更好的效能表現和散熱效果。

Q2: 台積電在先進封裝的優勢?

A: 擁有完整技術、高良率和量產經驗, 已是全球領導廠商。

關鍵字:半導體產業鏈、CoWoS、3DIC、台積電、AI 晶片、HPC、晶圓製造、封裝技術、先進封裝、Chiplet、摩爾定律、NVIDIA AI 晶片